32.Q2a: 有限状态机2(FSM)

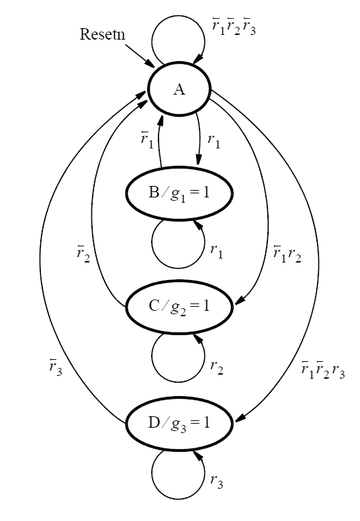

考虑以下状态图描述的FSM(有限状态机):

此FSM充当一个仲裁电路,控制三个请求设备对某种资源的访问。每个设备通过设置信号r[i] = 1来请求资源,其中r[i]可以是r[1]、r[2]或r[3]之一。每个r[i]都是FSM的输入信号,代表三个设备中的一个。只要没有请求,FSM就保持在状态A。当有一个或多个请求发生时,FSM决定哪个设备获得资源使用权,并转移到一个状态,该状态设置该设备的g[i]信号为1。每个g[i]都是FSM的输出信号。存在一个优先级系统,设备1的优先级高于设备2,而设备3具有最低优先级。因此,例如,只有当FSM处于状态A且仅有设备3提出请求时,设备3才会收到授权。一旦设备i被FSM授予权限,只要其请求r[i] = 1,该设备就会持续获得授权。

编写完整的Verilog代码来实现这个FSM。如同讲座中所做的一样,为状态表和状态触发器分别使用独立的always块。使用连续赋值语句或一个always块(根据你的判断)来描述FSM的输出g[i]。你可以自由地分配任何你希望使用的状态码。

模块声明

module top_module (

input clk,

input resetn, // active-low synchronous reset

input [3:1] r, // request

output [3:1] g // grant

);